This is an open access article distributed under the terms of the Creative Commons Attribution 4.0 International License (CC BY 4.0), which permits use, distribution, and reproduction in any medium, provided the original publication is properly cited. No use, distribution or reproduction is permitted which does not comply with these terms.

# NODE RINGING REDUCTION OF SYNCHRONOUS BUCK CONVERTER

Michal Frivaldský<sup>1,\*</sup>, Marcel Pčola<sup>2</sup>, Zdeno Biel<sup>2</sup>, Roman Kučera<sup>2</sup>, Marek Franko<sup>2</sup>, Roman Holček<sup>2</sup>

<sup>1</sup>Faculty of Electrical Engineering and Information Technologies, University of Zilina, Zilina, Slovakia <sup>2</sup>EVPU a.s., Nova Dubnica, Slovakia

\*E-mail of corresponding author: michal.frivaldsky@feit.uniza.sk

Michal Frivaldský (D 0000-0001-6138-3103,

Marek Franko D 0000-0003-1829-6455

#### Resume

This paper discusses the issue related to the switching regulators operated at high switching frequencies, where it is necessary to eliminate the influence of parasitic components of the converter's main circuit. In more detail it deals with the node-ringing phenomena, which is typical for synchronous buck converters. The existence of the parasitic inductances arising from the printed circuit board conductive paths, induce voltages, which are several times higher than nominal input voltage, thus it increases the risk of damage of the power transistors. Therefore, optimization of the circuit is required to reduce the voltage spikes and therefore improve safety margin related to nominal operation. In this paper, node-ringing phenomena is introduced, while the optimization methodologies for its reduction are described and verified by experimental analysis.

### Article info

Received 24 May 2023 Accepted 13 June 2023 Online 22 June 2023

### Keywords:

power transistor switching noise parasitics snubber

Available online: https://doi.org/10.26552/com.C.2023.054

ISSN 1335-4205 (print version) ISSN 2585-7878 (online version)

### 1 Introduction

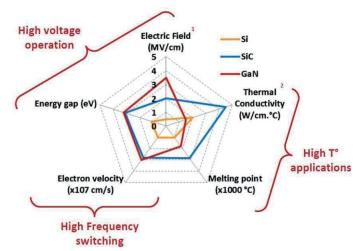

Current situation in the field of power electronic systems records massive expansion concerning breaking the usual trends. Here we are talking about development of the power semiconductor devices, while significant results are being achieved in terms of performance improvements, as well. The silicon carbide (SiC) is currently leading technology for high-voltage applications, such as electric vehicles, power supplies, motor control circuits and inverters for renewables. This technology offers several advantages over the standard silicon-based power semiconductor devices (IGBT, MOSFETs), which have been used for a long time as the main solution, due to their cost-effectiveness (Figure 1). Due to increasing demands on power density and efficiency of the power systems, the advent of new technological solutions represents a natural process of modernization of all the conventional, as well as specific performance electronic systems [1-3].

Designers of new, more demanding applications such automotive electrical systems and electric vehicles concluded that the new SiC and GaN technologies of power semiconductor structures, with their properties, are more suitable to achieve the desired results [4-5].

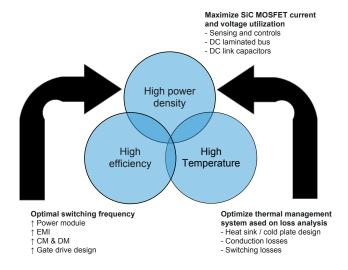

Just as modern technologies provide benefits, the use of modern devices also brings certain risk and pitfalls. As was mentioned, power - supply efficiency becomes increasingly important, meeting the high power densities means increasing the switching speed, so the negative trade-offs, like the electromagnetic interference, may occur (Figure 2). Here it is very sensitive issue, which is directly connected to practical design of any power converter, i.e. the printed circuit board (PCB) design represents the design challenge to prevent any unwanted phenomenon. In connection to requirements defined for modern power supplies, the high switching frequencies are required for their operation. One of the negative consequences when dealing with the PCB design and high frequency operation is generation of so-called node-ringing. Parasitic elements of the PCB or device package are responsible for transistor voltage node ringing, which should be optimized to prevent from damage of the component. The effects of these parasites are unexpectedly large and it often happens that a circuit, even if designed without problems, may

Figure 1 Comparison of the electrical and operational properties of Si, SiC and GaN technologies of power semiconductor devices

Figure 2 Diagram representing key demands on the switched mode power supplies

not operate properly, depending on the layout, due to insufficient attention being paid to these parasitic components [6-7].

In this paper, the focus is given on analysis of the node-ringing origin and its consequence regarding the power loss generation. The study is performed with synchronous buck converter, whose application is redundant power supply system. Initial analysis of the node-ringing is consequently modeled using verified circuit simulation model, while several methods how to the reduce node-ringing phenomenon are being described, as well.

### 2 Reasons of the node ringing generation

## 2.1 Main circuit description regarding the node ringing generation

Increasing number of industrial applications, require low output voltage/high current converters.

That is related to efficiency maximization, so the buck regulators are of interest when dealing with the power loss minimization. The high output current applications are specific, since the modular converters operated in parallel are utilized to reduce the thermal stress of power components. To be able to provide reliable and safe operation, the minimization of any negative phenomena is a must, while the node-ringing represents a major issue, which must be eliminated for buck regulators operating in a modular system.

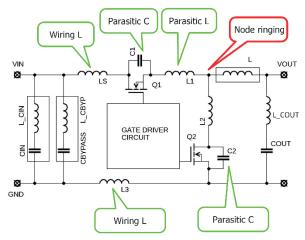

Figure 3 shows the principal schematics of synchronous buck converter including the parasitic components of the main circuit. Those are inductances of wirings of PCB and capacitances, which are parasitic components of power transistor itself. The presence and the effect of these parasites is the matter of this research, more precisely the way how to reduce their impact is the main issue. During the converter operation, they are responsible for unwanted oscillations of voltage and current waveforms and the result is overvoltage and overcurrent spikes generation, which negatively affect

${

m C50}$

Figure 3 Principle schematic of synchronous buck converter including the parasitic components

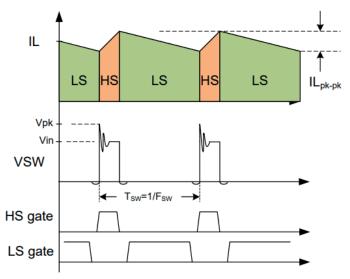

Figure 4 Time waveforms of synchronous buck converter indicating the node-ringing voltage

the electromagnetic interference of the power system.  $\,$

Figure 4 shows time waveforms of converter shown on Figure 3, introducing node-ringing effect, what is seen at the waveform of bottom power switch drain-source voltage.

The principal operation of the synchronous buck converter, operated in continuous conduction mode (CCM), considering nominal conditions, is based on the alternative high-side MOSFET and low-side MOSFET conduction of inductor current during each switching cycle. Cycle initialization is characterized by the green interval when low-side transistor is turned and is carrying the inductor current. After that, the LS MOSFET is turned off and the inductor current is freewheeling through the body diode of the low-side MOSFET. After a short dead time, the HS MOSFET switches on, starting the next conduction interval of inductor current. As the body diode undergoes reverse recovery, the voltage on SW begins to rise and the ringing waveform results from the interaction of parasitic inductances and the switch node capacitance (primarily consisting of the  $C_{\rm oss}$  of the low-side MOSFET) [8]. It must be noticed here that the overvoltage spike caused by node ringing can achieve multiples of the nominal blocking voltage of the transistor, thus possibly leading to its destruction. The amount of this spike directly depends on the value of parasitic inductances of wirings and the reverse recovery of used power semiconductor component [9].

Secondarily, the node-ringing effect affects the operational efficiency of the converter itself, therefore it is worth to deal with the elimination or reduction of the causes that are responsible for the generation of this undesirable phenomenon.

### 3 Physical prototype of analyzed synchronous buck regulator

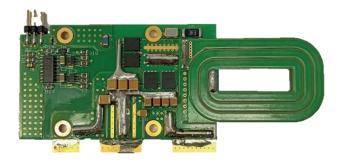

Analyzed converter topology is synchronous buck rectifier with interleaved topology. Figure 5 shows the physical prototype of one synchronous buck module,

Figure 5 Module of power converter

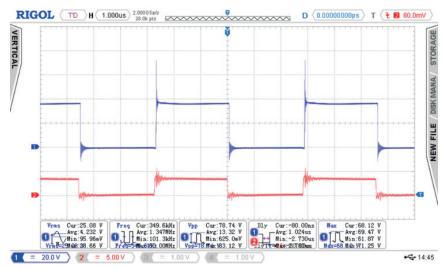

Figure 6 Drain to source voltage waveform (top) for nominal power of synchronous buck regulator module from Figure 5

while when it serves for the modular PSU design it contains two. The phase delay between switching of those modules is  $180^{\circ}$  to reduce the output voltage and current ripple. The modular PSU is designed for supplying the high-power ASIC microchips or high power MCU's where the low voltage and high currents are requested. The modules are constructed on the 6-layer FR4 printed circuit board, where the thickness of internal copper layers is 105  $\mu m$  and external layers are plated to thickness of 130  $\mu m$ . The bottom side of PCB is equipped by aluminum heatsink for cooling the power transistors.

Basic parameters for one module:

- Nominal input voltage: 36 V

- Output voltage: 12-22 V

- Maximal output current per module: 35 A

- Maximal output power per module: 600 W

- Maximal eficiency of module: 98.8%

- Power transistors: 027N10N6 (Infineon)

The complete PSU contains 3 channels (6 power modules) where the maximal output power of one channel is 1200 W and then the maximal output power of whole PSU is 3600 W. As described earlier, the node ringing is one of the problematic issues, which needs to be optimized in buck synchronous regulators. For designed physical sample, measurement of the drain-source voltage of the low-side transistor (Figure 6)

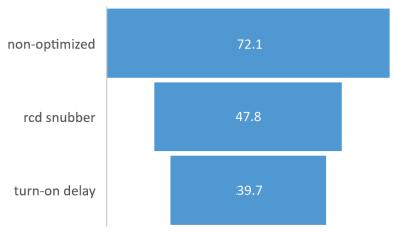

indicates, that the optimization should be performed here, as well. The value of the voltage spike, generated on the low-side transistor, is twice the value of the input voltage, i.e. 72 V. In the next part of this paper, two alternatives for optimization are being analyzed, while efficiency of the converter and drain-source voltage peak reduction are the main variables, which are evaluated.

### 4 Simulation analysis of the node ringing reduction

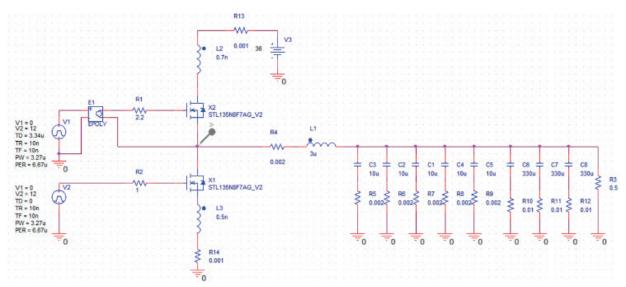

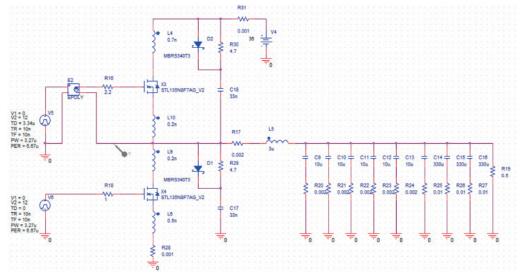

For the purposes of evaluation, which procedure represents effective solution for the node ringing reduction, it was decided to design the verified simulation model with high level of accuracy [10-12]. For this purpose, the development of the PSpice circuit was performed utilizing highly accurate models of power transistors (ST microelectronics - STL135N8F7AG), which are equipped within physical prototype, as well. The simulation model of the main power circuit is shown in Figure 7. Main circuit contains parasitic components as well, which are responsible for the node ringing generation (stray inductances).

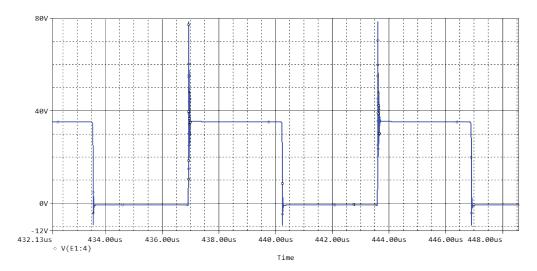

From initial simulation result (Figure 8) it is seen that the voltage spike, generated during the transistor switching, is reaching twice the voltage of the DC supply  ${ t C52}$

Figure 7 Simulation model of the considered synchronous buck regulator for the node ringing reduction analysis

Figure 8 Simulation result for the drain to source voltage waveform for nominal power of synchronous buck regulator module from Figure 7

Figure 9 Simulation model of the considered synchronous buck regulator with snubbers for the node ringing reduction analysis

voltage. Comparing this result to the measurement (Figure 6), it can be deduced that the result is verified and similar, so the optimization procedure would give the adequate results and information for the optimization needs. We have analyzed two methodologies for the node ringing reduction:

- Slowing the turn-on of the low-side transistor (25% slow down compared to non-optimized)

- Using the snubber circuits (for studied case: R = 4.7  $\Omega$ , C = 33 nF, D = MBRS340T3 Schottky)

According to the first method, reduction of the transistor switching speed may reflect within the increase of the total switching losses of the device, because the transition within the linear region of the volt-amp characteristics is lasting longer. Therefore, the optimal compromise between the reduction of ringing voltage and increase of switching loss must be met. Regarding the second method, it is expected that the power losses of the converter would increase due to fact, that the RCD snubber represents passive snubber circuit dissipating the energy coming from the noderinging oscillations.

The simulation experiments for the first method have been realized using schematics shown in Figure 8, while for the second method schematics from Figure 9 was used.

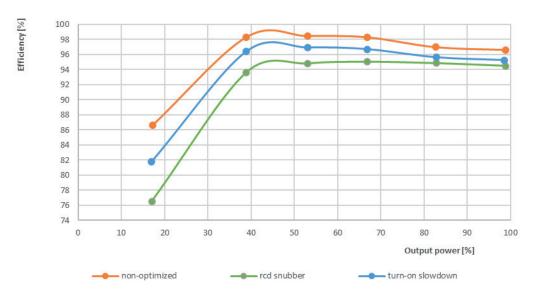

As was initially mentioned, two variables are under investigation, i.e. efficiency within the whole power range and drain - source voltage peak caused by the node ringing. Figure 10 shows dependency of the efficiency on output power, while the non-optimized converter is compared to applied methods for the noderinging reduction. It is seen from the results, that the highest efficiency is achieved for the non-optimized solution. The lowest value of the efficiency within whole power range states for the RCD snubber method, what reflects increased energy dissipation due to RCD snubber functionality, i.e., it dissipates the energy originating from the node ringing overvoltage. If slowing the lowside transistor turn on the process, higher efficiency is obtained, while for 100 %  $P_{\mbox{\scriptsize OUT}}$  , the value is 95.24 % what is 1.38% lower compared to non-optimized solutions and 0.73% higher compared to the RCD snubber result.

Figure 10 Efficiency dependency on the output power of the studied converter for the non-optimized sollution and two investigated approaches

Figure 11 Voltage spike value for individual study cases

${

m C54}$

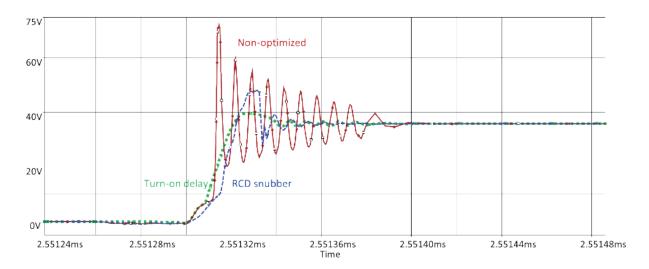

Figure 12 Time waveform of node-ringing voltage for studied converter and optimization methodologies

Figure 11 is showing evaluation of the results related to the drain-source peak voltage for the low side transistor of synchronous buck converter. The nominal input voltage is 36 V, while from the results it is seen that the non-optimized solution reached twice the value of input voltage. Considering the RCD snubber, the reduction of the voltage spike by 34% was achieved, while for the turn-on delay method, reduction reached 45%. The time waveforms comparison of these results is shown in Figure 12.

### 5 Conclusion

In this paper, the verification of methodologies for the node-ringing reduction has been the main focus of interests. Initially, discussion, related to the current progress within the power semiconductor technology development, was provided; followed by the description of the synchronous buck converter, the phenomena of node-ringing generation were introduced, as well. It was presented that this issue is dangerous considering the overvoltage damage of the power transistor used within the main circuit. Optimization for reduction is therefore required, while several methodologies are already available. Instead of the printed circuit board layout optimization, there are also other methodologies, which are based on the circuit modification. Here two alternatives have been verified. Once the prototype of the power converter was presented, the node-ringing voltage was measured as well to see the amount of overvoltage generation. The voltage spike reached twice the value of the input voltage of the converter. This result shows, how important it is to prevent from overvoltage damage, when the node-ringing is present. Another issue is electromagnetic emissions (EMI) optimization as well. The evaluation of the optimization methodology influence was provided through the verified circuit simulation model. We investigated the RCD snubber application and methodology, which is characterized by the turn-on slowdown of low-side transistor. The achieved results evaluated the efficiency performance for individual study cases and the amount of voltage spike reduction. From the results is seen that the turn-on slowdown improves voltage spike reduction by 45% compared to the non-optimized solution. On the other hand, it was negatively reflected in the reduction of efficiency by almost 1.4% compared to the non-optimized solution. As a conclusion it must be deduced that the node-ringing phenomena is unwanted as it harms the performance of the converter, from the EMI point of view, as from the safe and stable operation.

### Acknowledgment

This publication was realized with support of Operational Program Integrated Infrastructure 2014 - 2020 of the project: Innovative Solutions for Propulsion, Power and Safety Components of Transport Vehicles, code ITMS 313011V334, co-financed by the European Regional Development Fund.

### **Conflicts of interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

### References

- [1] SHAH, F. M., XIAO, H. M., LI, R., AWAIS, M., ZHOU, G., BITEW, G. T. Comparative performance evaluation of temperature dependent characteristics and power converter using GaN, SiC and Si power devices. In: 2018 IEEE 12th International Conference on Compatibility, Power Electronics and Power Engineering CPE-POWERENG 2018: proceedings [online]. IEEE. 2018. eISSN 2166-9546, p. 1-7. Available from: https://doi.org/10.1109/CPE.2018.8372523

- [2] SKAROLEK, P., LETTL, J. Influence of deadtime on Si, SiC and GaN converters. In: 2020 21st International Scientific Conference on Electric Power Engineering EPE: proceedings [online]. IEEE. 2020. eISSN 2376-5631, p. 1-4. Available from: https://doi.org/10.1109/EPE51172.2020.9269208

- [3] ZHANG, Y., XIAO, M., MA, Y., CHENG, K. 10 kV GaN power diodes and transistors with performance beyond SiC limit. In: 2022 6th IEEE Electron Devices Technology and Manufacturing Conference EDTM: proceedings [online]. IEEE. 2022. eISBN 978-1-6654-2178-2, p. 113-115. Available from: https://doi.org/10.1109/EDTM53872.2022.9797920

- [4] AL-BAYATI, A. M. S., ALHARBI, S. S., ALHARBI, S. S., MATIN, M. A comparative design and performance study of a non-isolated DC-DC buck converter based on Si-MOSFET/Si-Diode, SiC-JFET/SiC-schottky diode and GaN-transistor/SiC-Schottky diode power devices. In: 2017 North American Power Symposium NAPS: proceedings [online], IEEE. 2017. eISBN 978-1-5386-2699-3, p. 1-6. Available from: https://doi.org/10.1109/ NAPS.2017.8107192

- [5] ALHARBI, S. S., ALHARBI, S. S., AL-BAYATI, A. M. S., MATIN, M. Design and performance evaluation of a DC-DC buck-boost converter with cascode GaN FET, SiC JFET and Si IGBT power devices. In: 2017 North American Power Symposium NAPS: proceedings [online]. IEEE. 2017. eISBN 978-1-5386-2699-3, p. 1-6, Available from: https://doi.org/10.1109/NAPS.2017.8107322

- [6] KANTAVARA, S., KUMMANEE, P., SAWACHAN, H., BILSALAM, A. high frequency interleave technique based on high step-up push-pull resonant converter modules. In: 2021 18th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology ECTI-CON: proceedings [online]. IEEE. 2021. eISBN 978-1-6654-0382-5, p. 918-921. Available from: https://doi.org/10.1109/ECTI-CON51831.2021.9454943

- [7] LIN, C., SONG, O., WANG, J. A new high efficiency and high power density 48V to 1V converter. In: 2021 IEEE 1st International Power Electronics and Application Symposium PEAS: proceedings [online]. IEEE. 2021. 978-1-6654-1360-2, p. 1-3. Available from: https://doi.org/10.1109/PEAS53589.2021.9628611

- [8] AN-4162-switch node ring control in sznchronous buck regulators [online]. 2013. Available from: https://fairchildsemi.com

- [9] CHEN, Z., AMARO, I. Optimizing low side gate resistance for damping phase node ringing of synchronous buck converter. In: 2012 IEEE Energy Conversion Congress and Exposition ECCE: proceedings [online]. IEEE. 2012. ISSN 2329-3721, eISSN 2329-3748, p. 1827-1832. Available from: https://doi.org/10.1109/ECCE.2012.6342590

- [10] BOTTARO, E., CACCIATO, M., RAFFA, A., RIZZO, S. A., SALERNO, N., VENEZIANO, P. P. Development of a SPICE modelling strategy for power devices in GaN technology. In: 47th Annual Conference of the IEEE Industrial Electronics Society IECON 2021 [online]. IEEE. 2021. eISSN 2577-1647, p. 1-6. Available from: https://doi.org/10.1109/IECON48115.2021.9589710

- [11] NARDO, D., SCUTO, A., BUONOMO, S., CHIANTELLO, M., CACCIATO, M., SCARCELLA, G., RIZZO, S. A. GaN HEMT power losses modeling and evaluation in resonant LLC converters. In: 2022 IEEE Applied Power Electronics Conference and Exposition APEC: proceedings [online], IEEE. 2022. eISSN 2470-6647, p. 1637-1644. Available from: https://doi.org/10.1109/APEC43599.2022.9773758

- [12] CACCIOTTO, F., SCIORTINO, M., TERMINI, D., CACCIATO, M., RIZZO, S. A., SCELBA, G. Power loss modelling and efficiency optimization of a multi-output Flyback converter. In: 47th Annual Conference of the IEEE Industrial Electronics Society IECON 2021: proceedings [online]. IEEE. 2021. eISSN 2577-1647, p. 1-6. Available from: https://doi.org/10.1109/IECON48115.2021.9589886